**BARCO Projection Systems**

SECTION W

service sheet

# VIDEO INFORMATION

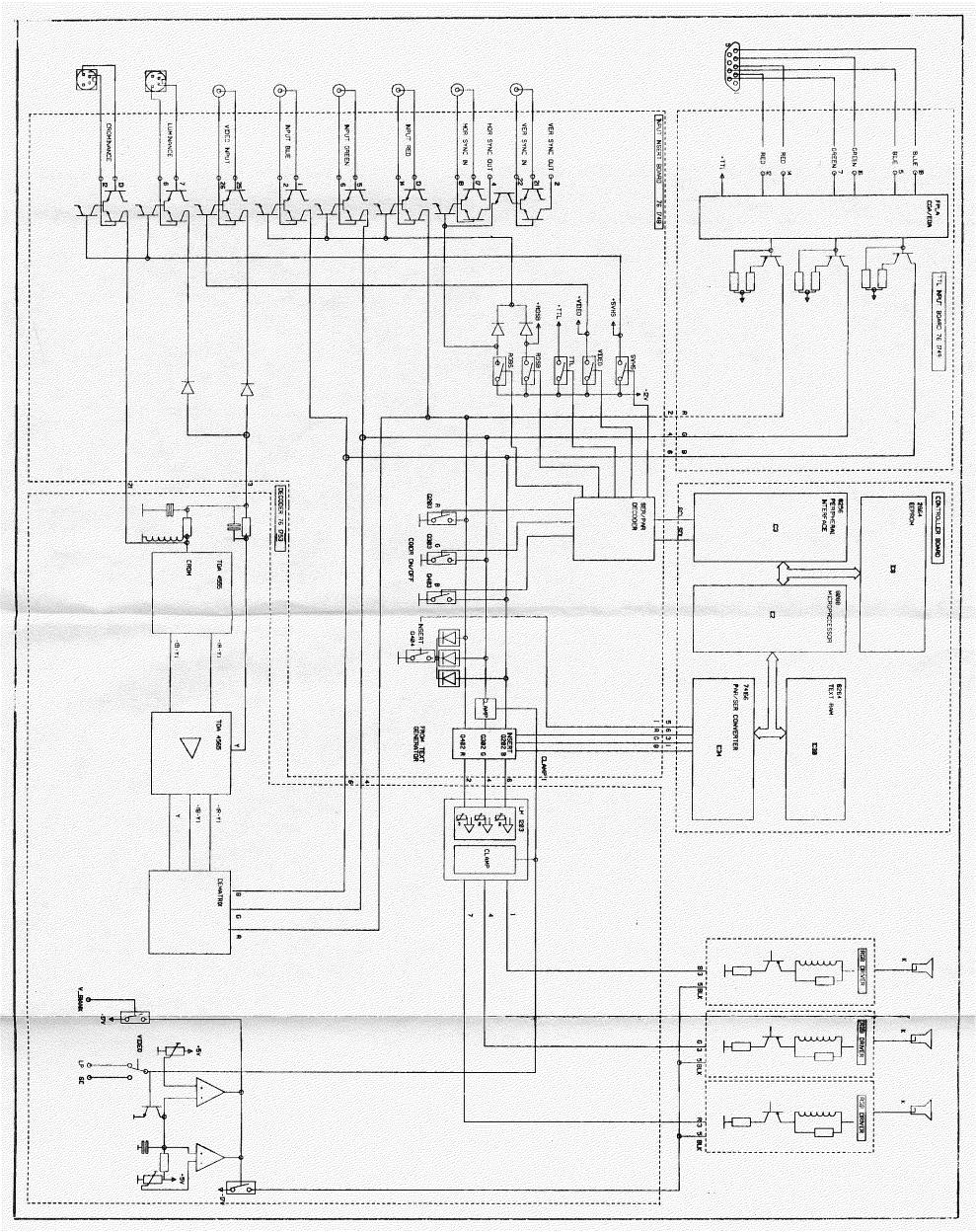

#### The video block diagram.

This text gives a brief description of all units, used to achieve an analog amplified clamped video output, which in turn controls the CRT cathode.

The following units can be distinguished:

- 761773 The Controller.

It generates I2C control signals to select a certain video source and it also includes a text generator.

- 761749 The TTL input board.

It converts the digital incoming RGB (EGA/CGA) signal to an analog RGB output.

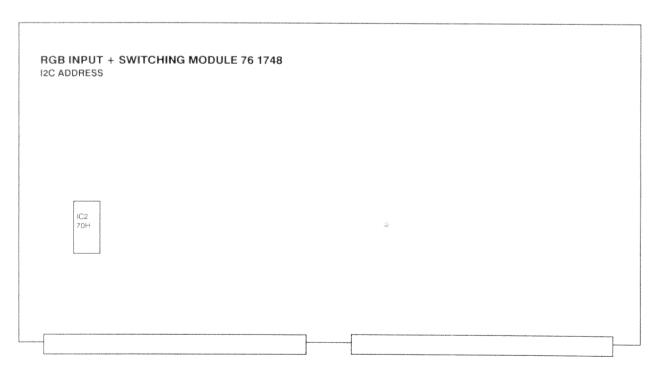

- 761748 The analog input board.

It makes a selection between the several input sources and clamps the green output, to insert text from the text generator.

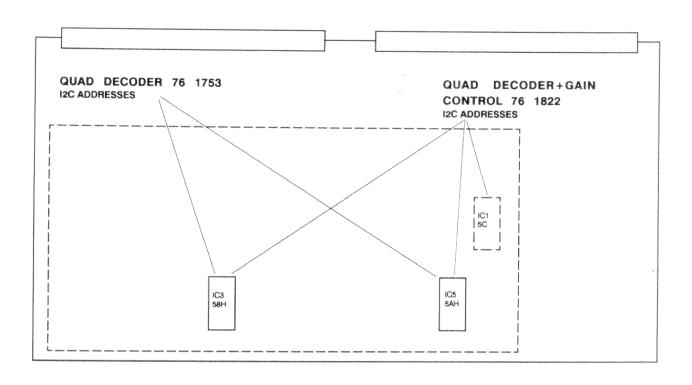

- 761753 The Decoder.

It converts the video information (Video/sVideo) into a analog RGB signal. It also contains the clamp pulse shaper, the video output amplifying + clamping circuitry.

- 761750 The CRT driver. It drives the cathode of the CRT

The controller. The heart of the digital projector is situated on the controller. It contains a 8088 uprocessor which gets its information out of an EPROM. The link with the several modules is established by using I2C communication, generated in a peripheral interface IC3. The controller unit contains also a text generator which adds text (control bars, warnings, menus) on the screen. The generators output consists out of a RGB and a control signal for Inserting text.

#### The TTL input unit

This unit receives a digital RGB input signal. It's generated by a computer and can be in CGA as well as EGA format. The modules output consists of current sources. The module is selected by the +TTL signal, coming from the analog input module.

# VIDEO INFORMATION

The RGB analog input unit.

Its major task is making the choice between the several input sources

- -TTL source

- Video source (luminance together with chrominance)

- SVHS source (chrominance separated from luminance)

- RGsB source

- RGBs source

The different sources are fed to differential amplifiers. Their current source is controlled by a switch (in fact switching transistors) which in turn is manipulated by the controller. The controllers I2C information is translated in a serial-parallel converter. Its outputs are used to control the different switches.

If the video information (VHS or SVHS) is selected, the video signal output is fed into the decoder module to attain an analog RGB signal. First of all the chrominance filtered out of the VHS signal. Afterwards the chrominance is separated into R-Y and B-Y signals by means of a TDA 4555. These signals, together with the luminance signal (Y) are amplified later on in the TDA 4565. At last the analog RGB signals are generated and delivered back to the RGB analog input module.

Each color output (R,G,B) of the selected source can be turned off, on controllers demand.(eg. for adjustment purpose)

When an information text, from the internal text generated, has to be added to the screen the Insert signal (I) becomes high. It pulls the external video information down and clamps the green output to be able to reinstall the right black level. The text information is added afterwards. The analog RGB output is amplified and clamped on the three colors afterwards an fed to the respective CRT cathode drivers.

# The blanking generator on the Decoder unit.

First of all the vertical blanking, generated on the vertical subunit, is used.

On the other hand, the horizontal blank is built up out of a capacitor which is forced to discharge through a transistor. The transistor is controlled by the sand-castle pulse (from vertical deflection unit) in case a video source is selected. Otherwise the horizontal flyback pulses (from the hor. defl. unit) are used instead. The capacitor voltage is fed to two OPAMPS to achieve left and right blanking. The among of blanking is adjusted by two digital potentiometers in IC5.

The CRT driver

Its major task is to charge or discharge the cathode capacitance to control the brightness of the CRT spots, making use of its input signal.

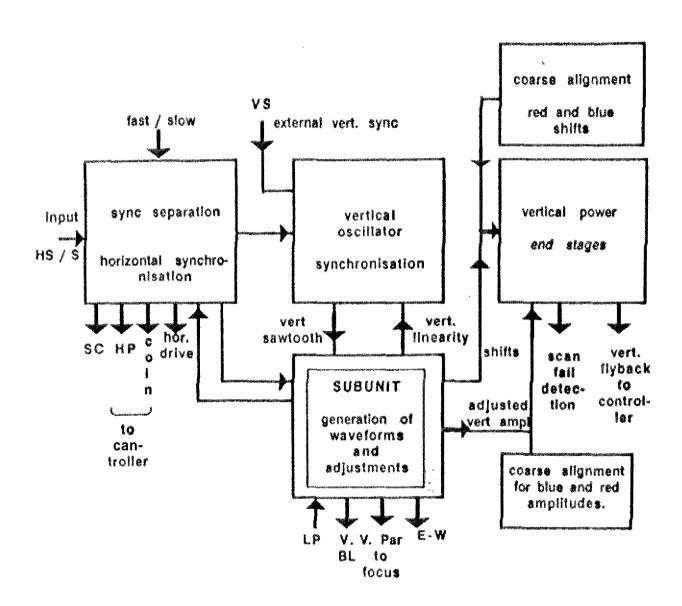

# VERTICAL DEFLECTION

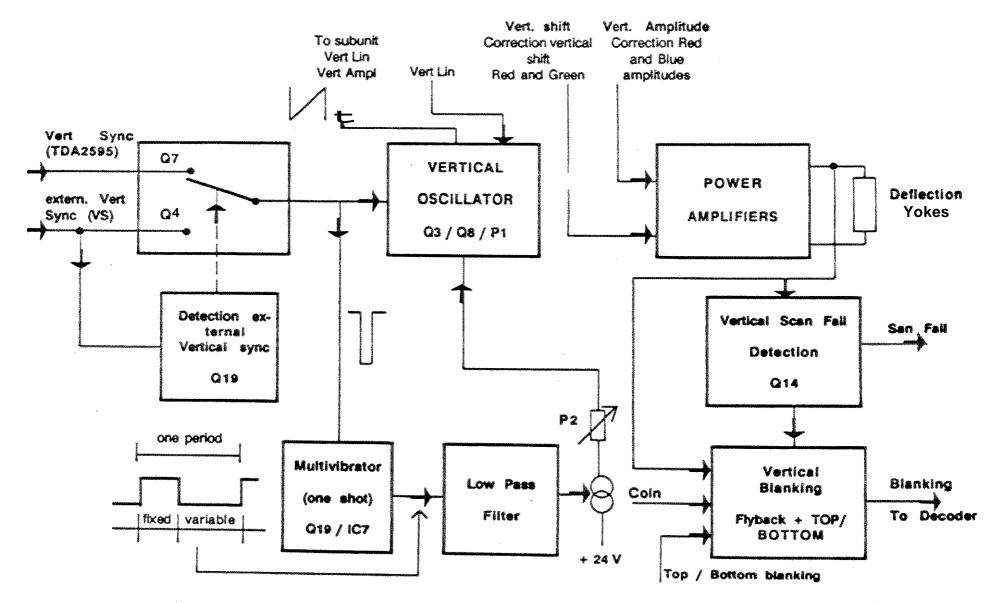

# The vertical deflection block diagram

As shown on the diagram the vertical raster circuitry is composed of several sub units outlined by dashed lines.

The following units can be distinguished:

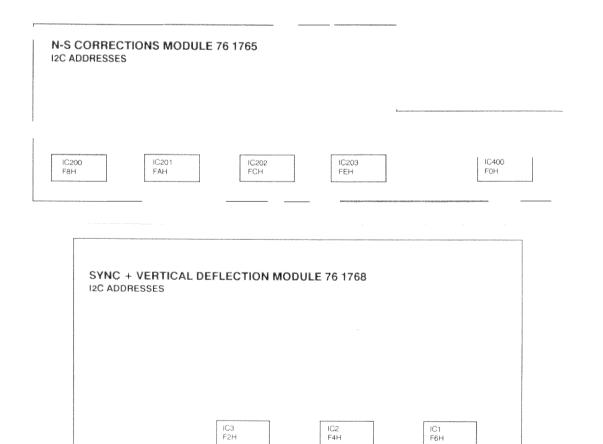

-S761765 The NS-correction unit (+ horizontal shift board)

It generates a sawtooth and parabolic wave form on horizontal line frequency for NS correction purpose. It also couples the NS-correction inductive to the deflection current.

#### -S761758 The NS-subunit

The geometric corrections are adjusted here, using the wave forms, generated on the NS-unit.

#### -S761768 The vertical deflection board

It contains an auto-locked oscillator which generates a sawtooth on vertical line frequency and three output amplifiers for the vertical deflection coils.

#### -S761769 The subunit vertical deflection

The DC output shift-current is adjusted here using IC5. It also generates the EW corrections and the top, bottom blanking.

#### -S761775 The main frame

Most of the connections between the several modules are implemented on the main Frame. It also contains the inversion switches.

#### The Vertical oscillator

The vertical oscillator is composed of C13,C14,Q3 and Q8. The capacitors charge to a certain vertical hold level, adjusted by a potentiometer. From that moment on Q3 and Q8 (= a FET configuration) conduct and discharge the capacitors immediatelly.

The horizontal/composit sync ,comming from the RGB analog input module 761748 (including video or luminance or int.hor sync or TTL hor sync or separated hor/comp sync), is fed into a video sync separator (2595) which delivers a composite sync output. It's integrated afterwards ,to neglect the horizontal sync pulses, and forces C13,C14 to discharge immediatelly which results in a synchronized vertical oscillator. The vertical hold potentiometer can be used to adjust the free running oscillator frequency by changing the vertical hold level.

A second way for synchronizing the oscillator ,which has the priority, can be achieved using an external separate vertical sync signal or the internal vertical sync which is also available on the RGB analog input board 761748.

# VERTICAL DEFLECTION

The oscillator output signal can be linearised using a feed back signal which is mainpulated by a digital potentiometer (marked with B: = Barco designed IC). That output is amplitude controlled afterwards, which in turn is fed into three separated vertical output amplifiers.

The DC output current is installed by three digital potentiometers (marked B) ,situated on the subunit in Ic5. It's used to shift the picture vertical. The output stages are connected to the inversion switches which in turn are connected to the deflection coils.

#### **NS-Corrections**

On the other hand, some corrections have to be added to the deflection current to correct the Top and Bottom bow and keystone errors. Therefore we generate a sawtooth, its inverse and a parabolic waveform, on horizontal scan frequency using the horizontal flyback pulses (350V PU) comming from the horizontal deflection board. The parabolic wave is achieved by multiplying the sawtooth with itself in a 1496 lc. These three waveforms are fed to the NS-subunit to be demultiplexed.

Due to the OPAMP (Ic4) configuration, the gate of the demultiplexer is set during the top part of the screen and reset during the bottom half screen part. The OPAMP gets therefore +6V on the non inverting input and the vertical sawtooth (VDB = vertical deflection blue) on the inverting input.

The demultiplexer outputs are manipulated by four potentiometers of Ic200(red),respective Ic201(blue) and 202(green). Two for the top and two for the bottom corrections. The common output is modulated on the vertical sawtooth (VDB) afterwards using Ic40,60 and Ic20. The modulator output current is then inductive coupled using a transformer ,in series with the deflection coil.

Three scan fail detections are included, to detect a failing vertical deflection output.

# HORIZONTAL DEFLECTION

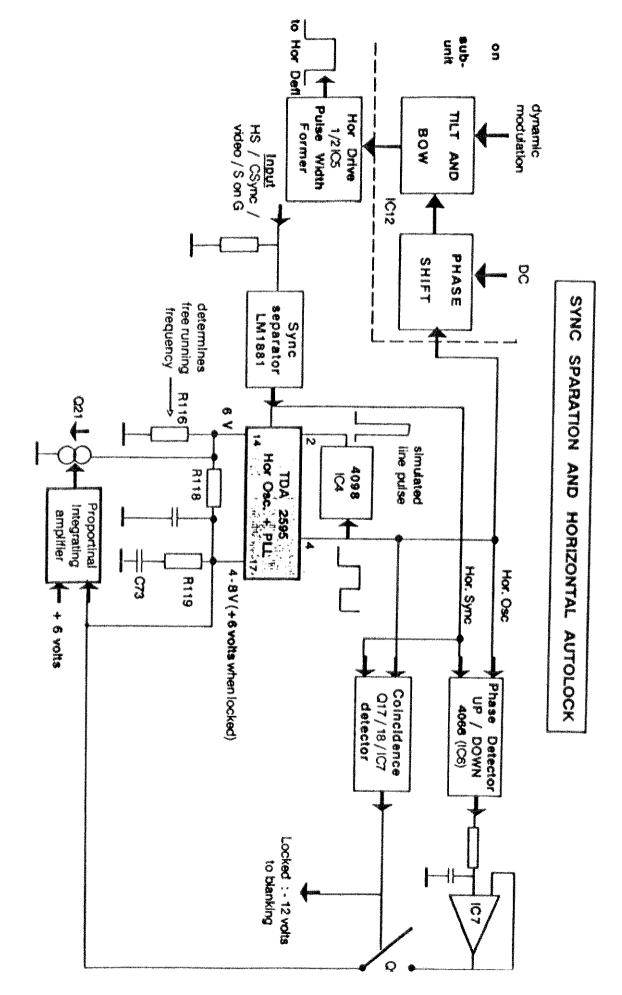

# The horizontal deflection diagram.

This diagram explains the horizontal deflection and all units needed to achieve a correct synchronized deflection.

The following units are implemented:

-761768 The vertical deflection board.

It generates the drive pulses for the horizontal oscillator

-761769 The vertical deflection subunit.

The EW and vertical midline bow and skew (using phase) corrections are derived here.

-761766 The horizontal deflection unit.

It includes the horizontal oscillator which is controlled by the drive pulses, and several protection circuits.

-761765 The NS-correction board.

It's used only to manipulate the DC-current in the horizontal deflection coils to achieve a horizontal shifting picture.

-761775 The main frame.

Most of the connections between several modules are implemented on the main frame. The inversion switches are also mounted on the frame circuit.

#### The drive pulses

The horizontal/composite sync, coming from the RGB analog input module 761748 (including video or luminance or int.hor.sync or TTL hor. sync or separated hor/comp sync), is fed into a video sync separator circuit 2595 as already mentioned in the vertical deflection description.

The 2595 includes a horizontal oscillator which must be tracked with the horizontal sync pulses. The internal phase comparator range is only 680 Hz, so larger frequency changes must be corrected with an external frequency correction circuit.

This is achieved by using two phase comparators. When the internal oscillator frequency gets too high, the PLL IC6 output becomes higher and activates Q9 through Ic7. The PLL output adjusts the oscillator through the conducting Q9.

On the other hand, when the internal frequency gets to low, the comparator Q17,Q18 will become low and Q9 will be activated again through Ic7. The PLL output will be able to adjust the oscillator again.

The synchronized horizontal pulses are converted to driving pulses by two one shots (IC5) and can be phase shifted by modifying the time constant of the first one shot.

# HORIZONTAL DEFLECTION

# The horizontal deflection oscillator.

The oscillator itself is described in detail in the text of module 761766 and isn't repeated here. It uses two mosfet switches, a recuperation capacitor C33, the diodes implemented in the mosfets, the deflection coil and a parallel capacitor. The drive pulses are used to control the mosfets.

The oscillator output is connected to the deflection coils through the inversion switch situated on the frame , together with a DC-shift current. The green shift signal is also fed to the Red and Blue circuit to attain a better Red on Green and Blue on green shift. The horizontal scan width of the three CRTs separately adjusted by means of the HOR WIDTH variable coils.

#### Protections.

The current through the mosfets is measured by taking the voltage over a wire resistance. The voltage controls Q21 which in turn activates a mono-flop. Its output pulls the drive pulses down.

Whenever the D-S voltage of the mosfets becomes dangerous high the output of Ic1 gets low and pulls the drive pulses down. This is nonreversal due to the feed back diode which locks Ic1.

A scan fail detection is also adapted to each CRT output

#### Power supply

The power supply situated on the horizontal deflection board is used to generate a 1000V voltage. It's used to protect the mosfets against a too high D-S switching voltage.

#### Geometric corrections

To correct the different geometric errors, the deflection current has to be modified. The vertical sawtooth, coming from the vertical oscillator, is fed twice in a multiplier Ic11 to generate a parabolic wave form on vertical raster scan.

The sawtooth and its inverse is used to correct the vertical midline skew, by modifying the phase of the driving pulses. The vertical keystone correction (EW) uses the same sawtooth signals but modifies the amplitude of the deflection current.

Bow corrections are similar achieved but use the parabolic wave form instead

To achieve an equal correction on several line frequencies, we have to modify the amount of correction. This is done by using the frequency dependent voltage \$V+, which is derived of the HTHD voltage on the horizontal deflection board.

**BARCO Projection Systems**

SECTION X

service sheet

**Cabinet Removal**

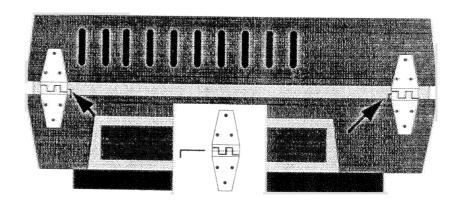

## Top cover removing

Pull out the two hinge-joints at the rear of the projector

Unlock the top cover from the bottom cover by pushing the lock on both sides of the cabinet by means of a screwdriver

CABINET REMOVAL Date: 10/10/90 Page 1

# **Cabinet Removal**

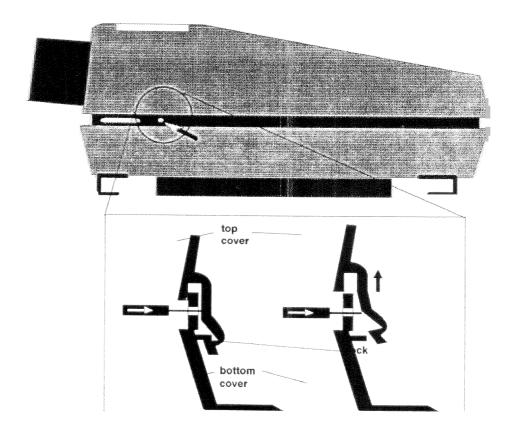

# Bottom cover removal

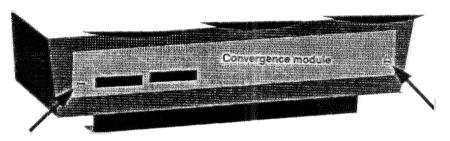

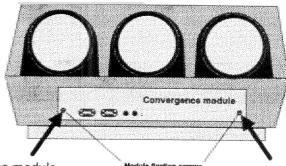

Remove the convergence module

Loosen the board fixation screws on both sides of the Convergence module

Pull out the Convergence module

Remove the two bolts inside the projector, at the left and the right side, which secure the bottom cover to the projector support.

For the same purpose as before, two bolts are provided at the rear side of the projector. To have access to one of the two bolts, the EHT module has to be removed.

Remove the two screws which secure the heatsink plate of the EHT board to the metallic main frame.

Pull the EHT module upwards to release the module connector from main frame connector.

Remove the two bolts, at the left and the right side, which secure the bottom cover to the projector support. (nutdriver 8mm).

Remove the three bolts, on each side of the projecor, which secure the metallic main frame to the projector support.

Lift projector assembly out of bottom cover

CABINET REMOVAL Date: 10/10/90 Page 3

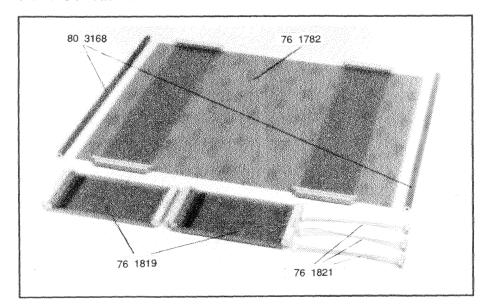

**SERVICE KIT** 98 27600

#### Introduction

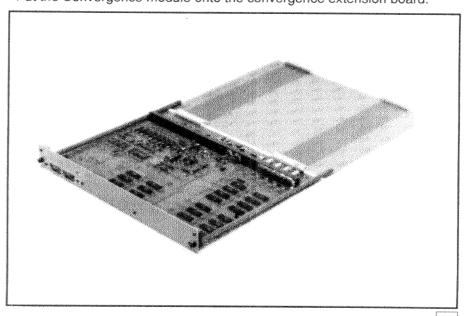

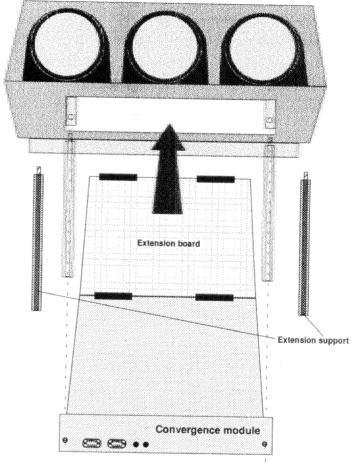

Repairing the Barco 800 series projectors on component level is made posible by using the extension boards and the extensions cable units, delivered as service kit.

#### Contents of the kit:.

Order No. kit: 98 27600

2 Extension boards for Euro cards:

1 Extension board for Convergence module:

2 Extensions metallic supports

3 Extension cable units:

Art. No. 76 1819 Art. No. 76 1782

Art. No. 80 3168

Art. No. 76 1821

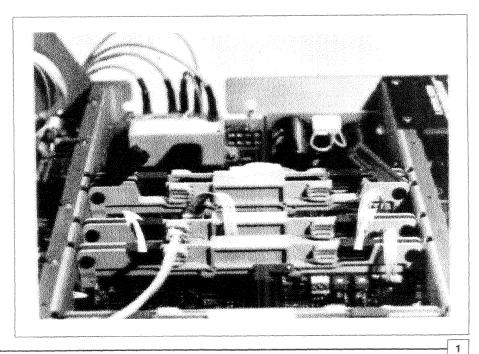

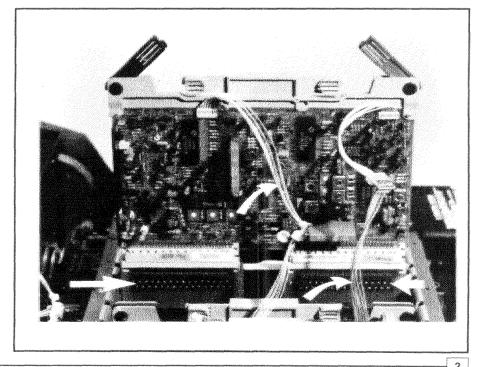

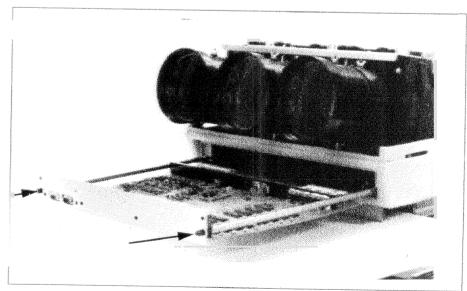

Using the extension boards for Euro cards

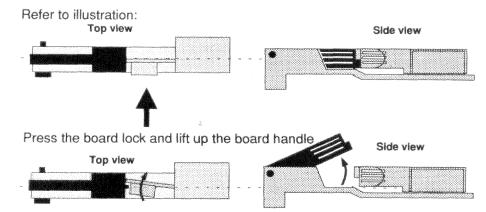

#### How to extract a module

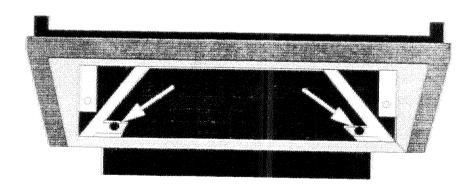

Each board is locked in the main chassis on both sides

Date: 09/10/90 98 27600 Service kit

SERVICE KIT 98 27600

To unlock the board, proceed as follows:

Repeat this action on both side of the module and extract the module out of the main frame.

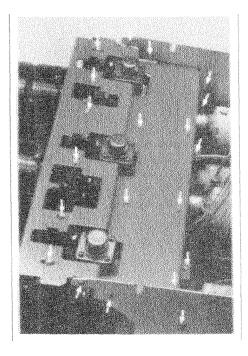

#### Example: repairing the decoder module

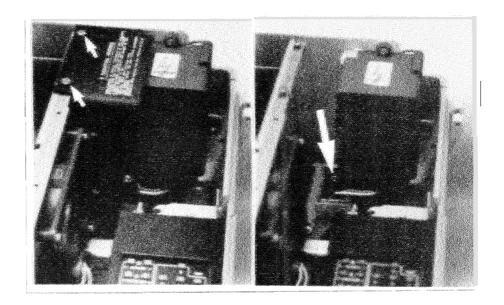

Unplug the two connection cables to and from the Decoder module

- Remove the Decoder module out of the main frame as already described.

- Plug the extension boards on the two decoder board connectors on the main frame.

Put the Decoder module on the extensions boards

- Reinstall the cable connection by inserting the extension cables.

**Important**: the extension board for Euro card is provided on each printed circuit foil with a measure contact.

Date: 09/10/90

SERVICE KIT 98 27600

Using the extension board for the Convergence module

# Removing the convergence module:

- Loosen the board fixation screws on both sides of the Convergence module.

- Pull out the Convergence module.

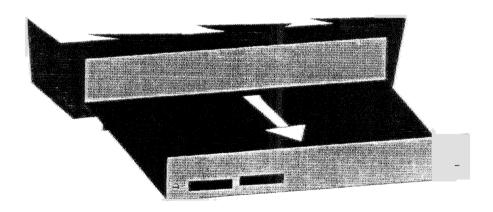

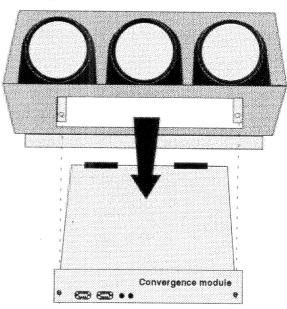

- Put the Convergence module onto the convergence extension board.

3

**SERVICE KIT** 98 27600

- Screw in on both side on the main frame the metallic extension supports.

- Slide the extension board with the plugged in Convergence module into the projector.

Secure the Convergence module onto the supports by screwing in the two remaining board screws.

Technical info-4 Date: 09/10/90 98 27600

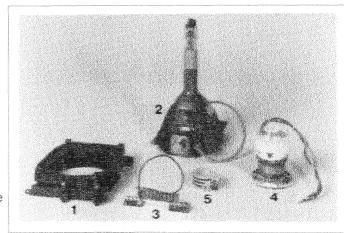

#### **WARNING: CRT HANDLING**

The picture tube encloses a high vacuum and care must be taken not to bump or to scratch the picture tube as this may cause the tube to implode resulting in personel injury and property damage. Shatter-proof goggles must always be worn by individuals while handing the CRT or installing it in the projector. Do not handle the CRT by the neck.

#### Mechanical disassembly

- 1. Top cover removal (see installation manual)

- 2. Loosen the retaining screws on both sides of the controller module.

- Turn this module 90°.

- Secure this position with the retaining screws.

- 3. Remove the CRT cover plate by :

- turning out the 20 bolts (nutdriver 7 mm and 8 mm)

- Remove the cover plate by lifting up.

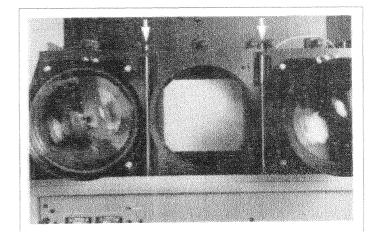

- 4. Remove the lens of the defective tube by :

- supporting the lens by hand when removing the bolds.

- turning out the 4 bolts of this lens (nutdriver 8 mm)

- sliding the lens to the front of the projector.

Date: 01/10/90

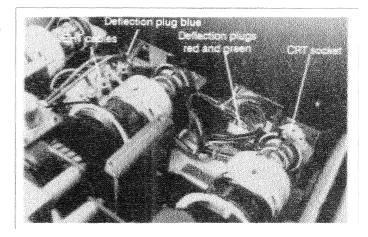

#### 5. Electrical disconnection of:

- EHT cables by turning the cap anti clockwise to unlock.

- black groundwire connected to the CRT socket (not visible on image)

- deflection plug.

- CRT socket by pulling back the CRT socket off of the end of the CRT.

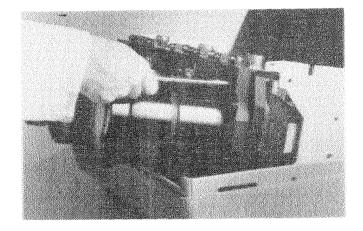

#### 6. CRT unit removal:

#### For Red and Blue:

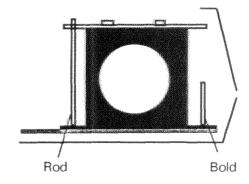

- turn out the bold, securing the CRT block to the main frame (see drawing).

- unscrew the rod on the other side of CRT block and pull it out.

- take out the defective tube.

#### For Green:

- unscrew the rods on each side of the green tube.

- pull out both rods.

- take out the defective tube.

Date: 01/10/90

#### CRT unit disassembly

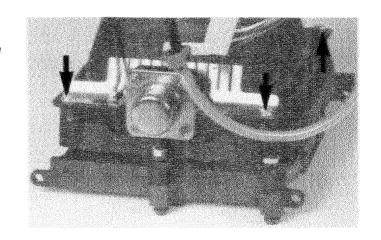

7. Remove CRT mounting block by screwing out the 4 bolts (nutdriver 8 mm).

- Loosen the 2pole/4pole magnetic ring retaining screw.

Slide off the 2pole/4pole magnetic ring of the end of theCRT.

- 9. Loosen the deflection yoke retaining screw.

Slide off the deflection yoke of the end of the CRT

#### Re-assemble the new tube.

- 10. slide carefully the deflection yoke <4> over the neck of the CRT <2>. Take care that the deflection wires are on the same side of the EHT connection.

- secure the retaining screw.

- 11.- slide now carefully the 2pole/4pole magnetic ring <5> over the neck of the CRT, against the deflection yoke.

- secure the retaining screw.

- 12.- place the tube <2> in the mounting block with the expansion tank to the top of the mounting block <1>

- positioning the akwadag plate <3>.

- screw in the 4 screws.

- Place the CRT unit in the projector. Expansion tank to the top.

Insert the fixation rodsand secure the side bolds (only for red and blue tube).

(see image next to item 6)

- 14. Re-install the electrical connections:

(see image next to item 5)

- EHT cable

- CRT socket

- deflection plug and black ground wire

- 15. Mount the lens and secure the four bolds

- 16. Put back the CRT cover plate and secure with the 20 bolds

- 17. Put in place the controller module

#### ADJUSTMENT PROCEDURE AFTER REPLACING A PICTURE TUBE

- \* Adjustment procedure valable for the three tubes, green, red and blue

- Raster centering (see owner's or installation manual)

- Lens focusing (see owner's or installation manual)

- Left-right, top-bottom focusing (see owner's or installation manual)

- \* Adjustments only for red and blue tube.

- Adjust the main shift adjustments on the Vertical deflection +sync module and North-south corrections module. (see procedure on the respective service sheet)

- CRT projection angle adjustment (see owner's or installation manual).

Adjustment of the 2 pole/4 pole magnet ring. (The adjustments have to be done separately for each CRT)

See Section CRT unit. Section I

Date: 01/10/90

**BARCO Projection Systems**

SECTION Y

service sheet

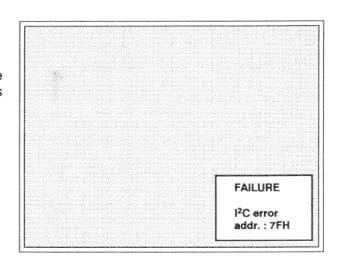

FAILURE I<sup>2</sup>C ERROR

$\mbox{\sc l}^2\mbox{\sc C}$  error is displayed on the screen together with the respective address, as illustrated on screen picture:

The table below indicates which IC corresponds to the displayed address . Replacement of the indicated IC solves the  $\rm I^2C$  error.

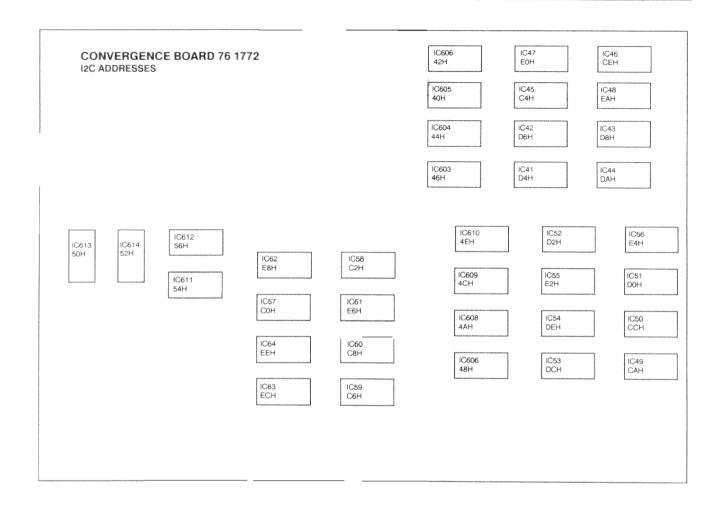

# Convergence module 761772

| Convergence module 761772 |       |                                |      |  |

|---------------------------|-------|--------------------------------|------|--|

| HEX address               | IC    | CORRECTION Red/Blue vert./hor. | ZONE |  |

|                           |       | •                              |      |  |

| COH                       | IC57  |                                | 1    |  |

| C2H                       | IC58  |                                | 2    |  |

| C4H                       | IC45  |                                | 3    |  |

| C6H                       | IC59  |                                | 4    |  |

| C8H                       | IC60  |                                | 5    |  |

| CAH                       | IC49  |                                | 6    |  |

| CCH                       | IC50  |                                | 7    |  |

| CEH                       | IC46  |                                | 8    |  |

| D0H                       | IC51  |                                | 9    |  |

| D2H                       | IC52  |                                | 10   |  |

| D4H                       | IC41  |                                | 11   |  |

| D6H                       | IC42  |                                | 12   |  |

| D8H                       | IC43  |                                | 13   |  |

| DAH                       | IC44  |                                | 14   |  |

| DCH                       | IC53  |                                | 15   |  |

| DEH                       | IC54  |                                | 16   |  |

| E0H                       | IC47  |                                | 17   |  |

| E2H                       | IC55  |                                | 18   |  |

| E4H                       | IC56  |                                | 19   |  |

| E6H                       | IC61  |                                | 20   |  |

| E8H                       | IC62  |                                | 21   |  |

| EAH                       | IC48  |                                | 22   |  |

| ECH                       | IC63  |                                | 23   |  |

| EEH                       | IC64  |                                | 24   |  |

| HEX address               | IC    | CORRECTION Green vert./hor.    | ZONE |  |

| 40H                       | IC605 | 5                              | 22   |  |

|                           |       |                                | 3    |  |

| 42H                       | IC606 | ີວ                             | 8    |  |

|                           |       |                                | 17   |  |

| 44H                       | IC60  |                                | 13   |  |

|                           |       |                                | 12   |  |

| 1  | 2  | 3  | 4  | 5  |

|----|----|----|----|----|

| 6  | 7  | 8  | 9  | 10 |

| 11 | 12 |    | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 |

| 20 | 21 | 22 | 23 | 24 |

| 46H | IC60  | 14 |

|-----|-------|----|

|     |       | 11 |

| 48H | IC607 | 6  |

|     |       | 15 |

| 4AH | IC608 | 7  |

|     |       | 16 |

| 4CH | IC609 | 9  |

|     |       | 18 |

| 4EH | IC610 | 19 |

|     |       | 10 |

| 50H | IC613 | 4  |

|     |       | 23 |

| 52H | IC614 | 5  |

|     |       | 24 |

| 54H | IC611 | 20 |

|     |       | 1  |

| 56H | IC612 | 2  |

|     |       | 21 |

|     |       |    |

1

**FAILURE** I<sup>2</sup>C ERROR

| Vertical deflection + sync module 76 1768         |       |                                                                                                                   | Quad decoder module 76 1753 |                                            |                                                                             |

|---------------------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|--------------------------------------------|-----------------------------------------------------------------------------|

| HEX address                                       | IC    | CORRECTION                                                                                                        | HEX address                 | IC                                         | CORRECTION                                                                  |

| F2H                                               | IC3   | top blanking<br>vertical shift red<br>vertical shift green<br>vertical shift blue                                 | 58H                         | IC3                                        | saturation R-Y<br>saturation B-Y<br>tint<br>sharpness                       |

| F4H                                               | 1C2   |                                                                                                                   | ∞1                          | 5                                          | contrast<br>brightness<br>blanking left<br>blanking right                   |

| F6H IC1 keystone skew bow vertical centerline bow |       | RGB in + RGB switching module 76 1748                                                                             |                             |                                            |                                                                             |

|                                                   |       | bow                                                                                                               | HEX address                 | IC                                         | CORRECTION                                                                  |

|                                                   |       |                                                                                                                   | 70H                         | IC2                                        | red on/off                                                                  |

| N-S corrections + hor. shift 76 1765              |       |                                                                                                                   |                             | green on/off<br>blue on/off                |                                                                             |

| HEX address                                       | IC    | CORRECTION                                                                                                        |                             |                                            | sync fast/slow<br>input video<br>input s-video                              |

| F8H                                               | IC200 | top bow red<br>bottom bow red<br>top keystone red<br>bottom keystone red                                          |                             | rikanseppinaassassastas Prikks Scriptorask | input RGB TTL<br>input RGsB analog<br>input RGBS analog<br>internal pattern |

|                                                   |       | top bow green                                                                                                     | Quad decoder module 76 1822 |                                            |                                                                             |

| 1741                                              |       | bottom bow green<br>top keystone green                                                                            | HEX address                 | IC                                         | CORRECTION                                                                  |

|                                                   |       | bottom keystone green                                                                                             | 58H                         | IC3                                        | saturation R-Y<br>saturation B-Y                                            |

| FCH                                               | IC202 | top bow blue<br>bottom bow blue<br>top keystone blue                                                              |                             |                                            | tint<br>sharpness                                                           |

| FEH                                               | IC203 | bottom keystone blue<br>centerline bow blue<br>centerline bow red<br>centerline bow green<br>horizontal amplitude | 5AH                         | IC5                                        | contrast<br>brightness<br>blanking left<br>blanking right                   |

| F0H                                               | IC400 | horizontal shift red<br>horizontal shift green<br>horizontal shift blue                                           | 5C                          | IC1                                        | red gain<br>blue gain<br>red cut off<br>blue cut off                        |

SEE NEXT PAGES FOR LOCATION ON BOARD LEVEL OF THE INDICATED IC's

FAILURE I<sup>2</sup>C ERROR

3

Date: 01/07/91

FAILURE I<sup>2</sup>C ERROR

# ADDITIONAL INFORMATION

# **BG-800 COMPONENT CLASS**

# SYNC-VERTICAL DEFLECTION 76-1768

# INTRODUCTION

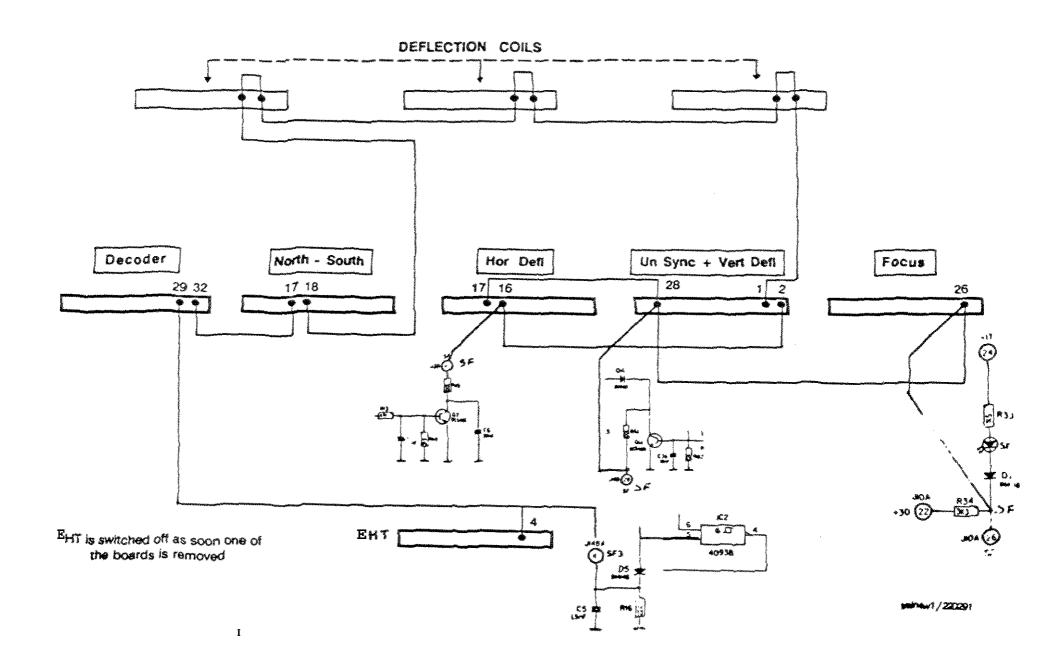

On this board and its sub-unit we find the sync separator, the autolock circuits, for driving the horizontal line and vertical oscillators, the vertical power output stages for all three vertical yoke circuits, and the preparation for the waveforms for the east-west correction signals.

The horizontal drive pulses for the MOSFET switchers on the Horizontal Deflection board are also prepared on this board.

A Barco designed IC called a "BELLA", comprising four (4) digitally controlled potentiometers, is utilized for the adjustment of the amplifude of the waveforms, or for some DC control voltage adjustments. These Bella IC's are used throughout the BG 800 for digital control of voltages and signals. This IC, custom made for BARCO, is driven by a I2C (serial data) bus from the microprocessor on the controller board.

## 1. THE VERTICAL OSCILLATOR

# a) Sawtooth Oscillator

The vertical sawtooth relaxation oscillator is built around Q3 and Q8 on the main Vertical deflection board. The 28VDC from the SMPS is regulated to 24V by IC8 and charges C13 and C14. As soon as the emitter voltage of Q3 reaches the voltage set by P1 (vertical hold 1) plus .6v, Q3 starts conducting and the collector of Q3 going in a positive direction, forward biases Q8 which also conducts. These two transistors form a discharge path for C13 and C14 to ground, and then the cycle can start all over again. This produces a Vertical Sawtooth waveform that free runs depending on the setting of P1.

# b) SYNCHRONIZATION OF THE VERTICAL OSCILLATOR

1) By means of composite sync:

The composite video or composite sync is applied to pin 2 of IC 14, a sync separator IC The composite sync output, from pin 1 of IC14 goes through emitter follower Q2 to pin

BG 800 COMPONENT SYNC VERT BOB CAROCHE TRG MGR. REV 2/92 11 of lc1. The composite sync also goes to Q1 base. The vertical positive going output pulses from IC1 pin 9 go to the base of Q7. The inverted vertical pulses from the collector of Q7 go through D7, C22 and then pull the base of PNP transistor Q3 negative, turning Q3 on. This action requires that Q6 is conducting at the time to form a emitter ground return for Q7.

The vertical oscillator can also be triggered by VS, separate vertical sync pulses injected into the projector at the VS BNC input, or the separate Vertical Sync that is used when the internal crosshatch or on screen display is selected. The separate vertical sync pulses enter the board at J4A-13, labeled VS on the schematic, then they are inverted by Q4 and trigger the vertical oscillator via D10 and D7. The negative sync pulses on the collector of Q4 also cause the gate of Q6 to be pulled low via D9, cutting off Q6. C23 keeps Q6 blocked as long as the negative pulses are on the gate of Q6. This keeps vertical sync pulses from passing through Q7 when separate vertical sync is utilized.

# c) " BELLA", BARCO MADE IC: FOUR SECTION DIGITAL CONTROLLED POTENTIOMETER

The voltage or waveform, applied between VRP and VRN is adjustable in 128 steps and is available at the output V0. ( refer to IC2, sub-unit, lower left of sub-unit schematic). The corresponding pins are:

VRP1 variable resistor positive 1 VRN1 variable resistor negative 1 VO1 variable out 1

There are four pots in each Bella IC, and three of these IC's on the Vertical sub-unit. IC1, IC2, and IC3.

The control of these IC's is accomplished with a SCL (serial clock), and SDA, (serial data) which come from the controller board. The address of the IC, (Ic number) is determined by the address pins that are grounded on each IC. The address determines the IC number, such as IC1, IC2 etc... and the slave address determines which pot, VO1, VO2 etc....

The lc is powered by VCC on pin 28, and VSS on pin 14. VCC is +5 volts DC measured from VSS.

## d) Vertical Linearity Control

The shape of the vertical sawtooth determines the linearity of the vertical sweep. This can be changed by means of a feedback circuit, feeding a sawtooth to C14 via R33. (coordinate I-1 main schematic). This sawtooth is adjusted in IC2 on the sub-unit, via

VRP1/VRN1/ VO1. This sawtooth comes from the main vertical board, transistor Q10 (J3-1 marked VST), goes to pin 19 of IC2 on the sub-unit, and comes out of IC2 on pin 25. It now goes through a buffer stage IC8, and returns to the main vertical board on J3-3 (marked Vlin on the main board), and through R33 to the junction of the vertical oscillator capacitors. This influences the charging behavior of C14, through R33, and therefore acts to change the linearity.

# e) The Vertical Autolock Circuit

This circuit is built around Q19, IC7 (pins 12, 13 and 14) and IC9 (pins 5, 6 and 7). The vertical sync pulses are picked up at the collector of Q7 and differentiated by C9 and R16. This would form a negative and positive pulse, and the positive pulse is used to trigger Q19. The negative pulse is grounded by D37. The output of the op-amp (IC7 pins 12,13, and 14) acting as a comparator, is fed back to the base of Q19 in order to keep it from retriggering after a trigger. R103, C30 determines the time constant of the circuit, before it can accept another trigger pulse. (negative in pin 12 of IC7 = negative pin 14, D38 clamps input)

The non-inverting input of IC7 is pulled up to 12 volts by R108 and a capacitor C31 is connected to ground. When no trigger pulses are applied to the base of Q19, pin 12 is at + 12 volts and the output is at +12 volts. When a vertical trigger pulse is applied at the base of Q19, C31 is discharged via Q19 and the output of IC7 pin 14 switches to -12 volts. This negative voltage is slightly delayed by C30, and this keeps the base low via D38 to prevent re-triggering. The capacitor C31 charges up to the 12 volts and when the voltage on the inverting and non-inverting inputs of IC7 are equal, the output switches high again. IC7 is then ready to accept the next trigger input, and the cycle starts over again.

The time between two consecutive vertical pulses determines the time the output is high, as the time the output is low is invariable and is set by the time constant C31/R108. The duty cycle of this squared waveform depends on the time between two consecutive pulses. This squared waveform is now clamped at ground by D35, so that only the positive portion of the waveform will charge the capacitors C62/C61. D34 and D36 provide a path for discharge of the capacitors in both directions for rapid equalization when changing vertical frequencies. This circuit acts as a variable chopper power supply, with the vertical frequency determining the output DC level. The C62, C61 network, acts as a double integrator, to change the pulsating DC to a varying DC voltage, Inversely proportional to the vertical frequency. This voltage is sent to pin 5 of IC9 (a buffer). When the vertical frequency increases, the voltage on C61 decreases due to the shorter duty cycle, and Q11 conduction decreases, and causes an increase in the charging current of C14 through Q12. This is due to the fact that when Q11 conduction decreases, there is a higher DC level at the emitter of Q12, causing Q12 to increase conduction. This causes a higher DC level at the collector of Q12. Basically Q12 and R23 are in

parallel from the 24 volt line to the vertical oscillator capacitors. When Q12 conduction increases, it's internal resistance is lowered and since the time constant of the vertical circuit is R23 times C13 and C14, a lowering of the parallel resistance of R23 and Q12 will decrease the time constant and cause the vertical sawtooth frequency to increase. The Vertical Hold 2, P2, allows an adjustment of the gain and thus the highest frequency that must be locked by the circuit.

# f) Vertical output stages, vertical shift, vertical amplitude.

The vertical sawtooth at the emitter of Q10 leaves the main vertical board from J3(1) and goes to the sub-unit to IC2 (VRN0 and VRP0 Vertical Amp Adjust) and the output leaves at VO0 (pin24), and returns to the main board through Q5 at J4 (4). It is now capacitively coupled to the inverting inputs of the power amplifiers iC11, IC12, and IC13 together with a DC voltage (vertical shift voltage). The vertical shift voltages are controlled by IC3 on the vertical sub-unit. (outputs 25, 26 and 27). The red and blue beam will follow the green shift, because a portion of the green shift voltage is fed to the red and blue shift lines. The shift voltages vary between +3V and - 1.7V. The sub-unit on the main board (coor. G-5) is used to fine tune the vertical blue and red shift, so that accurate center shift can be attained. The shift in terminal J4B12 is used, when the vertical scan is changed from ceiling mount to table mount. These two analog shift voltages are coupled with the voltages from IC3. (This sub-unit may not be present in older 800 Series projectors, however it can be added). This sub-board also contains 2 pots, P4 and P3. These pots can be used to adjust the red and blue vertical raster size to match the green raster. This adjustment should be done in the North South Geometry mode only.

The amplified sawtooth output currents flow in the respective scan coils and the ground return for these waveforms are the feedback resistors. R44, R97 and R79. The amplitude of the waveforms across these resistors is proportional to the vertical amplitude and thus, these voltages can be used for a feedback stabilization of the vertical output circuits.

The TDA 8172 allows for a short vertical retrace time by doubling the supply voltage during retrace. During the flyback the voltage across capacitors C35, C55 and C52 is switched in series with the supply voltage of +8v. As a result, the voltage during flyback is 8+(8+17)=33 volts. This increased voltage allows for a shorter flyback time.

## g) Vertical scan fail detection.

The flyback pulses at the pins 6 of the output amplifiers are AC coupled to a parallel detector. The diodes rectify the negative pulses and generate a negative 21 volts at the anode of the three diodes, ( D24, D22 and D28 ) when a flyback pulse is present. As soon as one of the output stages fail, the voltage on the corresponding capacitor looses it's negative charge and via the diode, the base of Q14 gets a supply voltage from the +17 volt supply through one of the resistors ( R88, R83 or R85) and Q14 turns on pulling

the scan fail line low, through D17. Diode D16 and the saturated Q14 cause a permanent conduction of transistor Q15, and the high generated at J4B (26) blanks the CRTs.

Vertical retrace blanking pulses are derived from the vertical flyback pulse at pin 6 of the red output stage (IC11) and fed to the base of Q20, and then to Q15. The Vertical Blanking pulse leaves the board at J4B (26).

# 2. EAST-WEST CORRECTION.

# a) Trapezoidal distortion correction.

The sawtooth waveform (VST) is applied to the buffer IC7 on the sub-unit via C14 (pin 10 of IC7). This signal is inverted by an invertor in IC7 (pin 12, 13 and 14), and the two opposite phase sawtooth's are fed into IC1 pins 16, 17, or VRN0 and VRP0. The corresponding VO0 output goes through R45 to the adder amplifier IC7 pins 5,6, and 7. R 43 also couples a parabolic waveform into this same adder.

# b) Parabolic or pincushion distortion correction.

The parabolic waveform is obtained by means of the multiplier IC11. The waveform at pin 8 of IC7 goes to pins 10 and 1 through capacitors C1 and C2. The opposite phase signal outputs of pins 6 and 12 are then capacitively coupled to the pins VRN2 and VRP2 of IC1. The adjusted output VO2 is now applied, together with the previously discussed sawtooth output to the adder IC7 pin 5. Part of the parabolic waveform also goes through Q3 and Q2, and exits Q2 emitter via R29 to J4 -10. This VPAR then goes to the focus board for electronic focus correction from top to bottom of the raster.

## c) Frequency dependent correction.

The gain of the Op-amp in IC7 pins 5, 6, and 7 is variable and depends on the divider R31/Q1. The FET Q1 is biased by the output of an Op-amp iC7 (pin 1). The integrated output of the E-W correction, pin 7, is applied to the Miller integrator input, pin 2 and the other input receives a portion of the HTHD voltage. The HTHD voltage is proportional to the line frequency. An increase of the line frequency, results in an increase of the voltage on pin 3 (+HTHD'). This results in an increase of the gain of the op-amp because the fet Q1 conducts more. This shunts the negative feedback to ground and increases the gain of the op-amp. Pin 2 follows this increase up to the point where both pins 2 and 3 have equal voltage. Through his method, we have a frequency gain correction for higher frequencies since we would need a larger signal at the higher frequencies.

BG 800 COMPONENT SYNC VERT BOB CARDONE TRG HGR.REV 2/92

# d) Power Amplifier.

The sum of the corrections are sent back to the motherboard to be amplified by IC10 pins 1,2, and 4. It is then sent to the horizontal deflection board to modulate the HTHD supply Via Q13 on the horizontal deflection board.

# 3. MIDLINE CORRECTION (bow and skew)

The midline bow and skew corrections are added to the phase control of the picture. These corrections are a dynamic correction of the phase at a vertical rate, in order to adjust the center vertical line. The sum of the sawtooth and parabolic waveforms, are added via R44 and R42 on the sub-unit, and are then sent to the op-amp in IC8 (pin 24 and pin 25 of IC1 to IC8 pin 2). From IC8 pin 1 they go to pin 15 of the monoflop in IC12. This monoflop is triggered by the horizontal pulse from IC12 pin 12. Depending on the waveform on IC12 pin 15 and HTHD on this same pin, Ic12 output on pin 4 will have a variable width pulse. The width of the pulse is dependant on pin 15's voltage. If we use the trailing edge of the pulse to key the next stage, it can be seen that we have a way of varying the phase. The time constant of the monoflop is dependant on:

- 1. The corrections sent via D16, the dynamic correction of the phase.

- 2. The scan voltage +HTHD'; in order to decrease the correction at higher frequencies. At the higher frequencies, the phase correction as related to time would have to be less, because the line period would be less, and the percentage of correction would have to remain the same.

#### 4. PHASE ALIGNMENT.

The phase of the picture is adjusted by introducing a variable delay of the horizontal drive pulses.

The adjustment range over the entire frequency range must be proportional with the line period.

if we have for example, a 6 microsecond range of phase shift at 15kHz, this would represent 64/6= 10% phase shift. The same 6 microsecond shift at 90 kHz would be 11/6= %50 phase shift, or half the picture. Consequently, the range must be much lower for 90 kHz compared with 15 kHz, or the range must be "tracked" with the line frequency. The DC voltage at VO2 (pin 26 of IC2) is the DC phase shift voltage and is sent to comparator Q7. The other transistor in Q7 receives the integrated drive pulses, thus a DC voltage related to the line period. (left side of Q7). The difference in voltage between the two collectors of Q7 becomes the base emitter voltage of Q6, or Q6 bias. Q6 is a current generator and part of the time constant of the monoflop in IC12. The width of the output pulse is controlled by the current generator Q6 and the monoflop, as long as the DC voltages at the bases of Q7 are not the same. This means that the width of the pulse ( =

phase shift) becomes smaller at higher frequencies, in order to decrease the phase shift at these higher frequencies.

The pulse train that inputs to pin 10 of IC12 comes from J3-5 ( HP In). This Hp in horizontal pulse comes from the main board, IC1 pin 4( J4 pin2 labeled HP out on main board). The horizontal pulse enters IC12 pin 10, and the variable width pulse exits IC12 pin 12 and goes to IC12 pin 2. Between IC12 pin 2 and Ic12 pin 4, the Vertical centerline skew and bow are adjusted, and that variable width pulse exits IC12 pin 4. Next, the signal goes through Q8 at pin 12 of IC12 and is then sent to the main board of the unit and then to IC5, pin 11( marked J4-2 HP In). IC5 monostable now produces a horizontal drive pulse with a constant ( 2uS) width, that will drive the MOSFETS on the UN Deflection Board (HDR).

## 5. HORIZONTAL OSCILLATOR- HORIZONTAL AUTOLOCK

# a) Horizontal autolock

The sync separator IC14, (which is really a sync stripper) on the main board sends Q1 a composite sync signal (both horizontal and vertical sync). The amplified signal is then split to the PLL (IC6) and transistor Q17. The oscillator in the TDA 2595 is locked to the exact frequency by a PLL, but the latter has only a limited lock range of approximately 1.2 kHz. Therefore it serves as a fine lock for the frequency. An additional PLL, IC6 is used to coarse lock the frequency range from 15 to 90 kHz.

IC6 consists of two phase comparators and a VCO (voltage controlled oscillator). For this application, only the second phase comparator is used. The signal input, (pin 14 of IC6) is the line oscillator of the TDA 2595 (IC1), and the comparator input (pin 3) is the sync pulses buffered by Q1. The corresponding output is pin 13.

Note that it is a three level output and thus a pulsed information source. If the output is "open", (in the locked state) the voltage is set at 6 VDC with R92/R89. On the other hand, pin 6 of IC7 is set at 7.7 VDC with R94/R90.

In the locked state, the FET( behaving as a switcher) Q9 is blocked, because the output pin 7 of the voltage comparator IC7 is "low". Indeed the PLL output is 6 volts, thus pin 5 is lower than pin 6 and the output is "low". When Q9 is blocked, the coarse frequency correction circuit is in effect disconnected from IC1.

# b) Line oscillator lower than the horizontal sync frequency.

If we assume that the horizontal frequency is lower than the horizontal sync pulse frequency, then the voltage on C8 decreases (pull down state). The output voltage on IC6 pin 13 will track the line frequency versus the sync frequency. If the line oscillator is at 15kHz and the sync is at 33 kHz, pin 13 will go low. This voltage is

now buffered and sent to pin 5 of IC7. Because of the Zener Z3, this voltage cannot decrease and stays at approximately 6V. The other pin, pin 6 is initially at 7.7v (divider R90/R94). This voltage now decreases because transistor Q17 discharges the capacitor C50 as follows:

The squared horizontal drive of pin 4 of the TDA 2595 switches Q18 on and off. When the frequency of the line oscillator is different from the horizontal sync (as we assume), these pulses arrive on the base of Q17 at the moment Q18 is off. These horizontal sync pulses switch on Q17 and C50 is discharged. The voltage at pin 6 drops and becomes lower than the other input on pin 5. The output on pin 7 of IC7 switches "high". The gate of the MOSFET Q9 is now positive and Q9 conducts and connects the output pin 8 of the PLL (IC7) to the inverting input, pin 2, of the next integrating op-amp (IC7 pins 1,2,and 3). The decreasing voltage output of the PLL is inverted and transistor Q21 draws more current out of pin 14 of IC1 (TDA 2595). This increases the frequency of the line oscillator. (IC1 pin 14 voltage is inversely proportional to the frequency. I.E., If Q21 turns on hard, it's collector goes low, and the oscillator frequency in IC1 will Increase).

As the frequency of the line oscillator increases, the PLL output also increases equally. This continues until there is coincidence between the horizontal drive and the horizontal sync at the base of Q17. Once coincidence is reached, the voltage at pin 6 is again 7.7 volts and the Mosfet Q9 changes to a blocked condition.

From this point on, the fine frequency lock in the TDA 2595 takes over and adjust the line oscillator until the exact frequency and phase is reached. The output line of the TDA 2595 pin 17, then feeds IC7 pin 2, and the fine frequency loop is established. In the locked state this PLL output is 6 volts. Since pin 3 of the op-amp is biased at 6 volts, the action of the op-amp continues up to the moment the oscillator is locked. Any small change in frequency after it is locked, is handled internally by the TDA 2595.

## c) Line oscillator higher than the horizontal sync.

In this case the PLL output is increasing, Z3 cannot perform it's zener function, and pin 5 of IC7 follows the PLL output voltage, or goes in a positive direction. Again, because there is no coincidence, the voltage at pin 6 is decreasing because the sync pulses are triggering Q17, and pulling it's collector low. This again turns on the FET Q9, so the coarse loop is connected. Now the "high" on IC7 pin 8 is coupled through Q9 to Ic7 pin2, inverted to a low and used to reduce the forward bias on Q21. This causes Q21's collector to go high, and thus, lower the horizontal frequency.

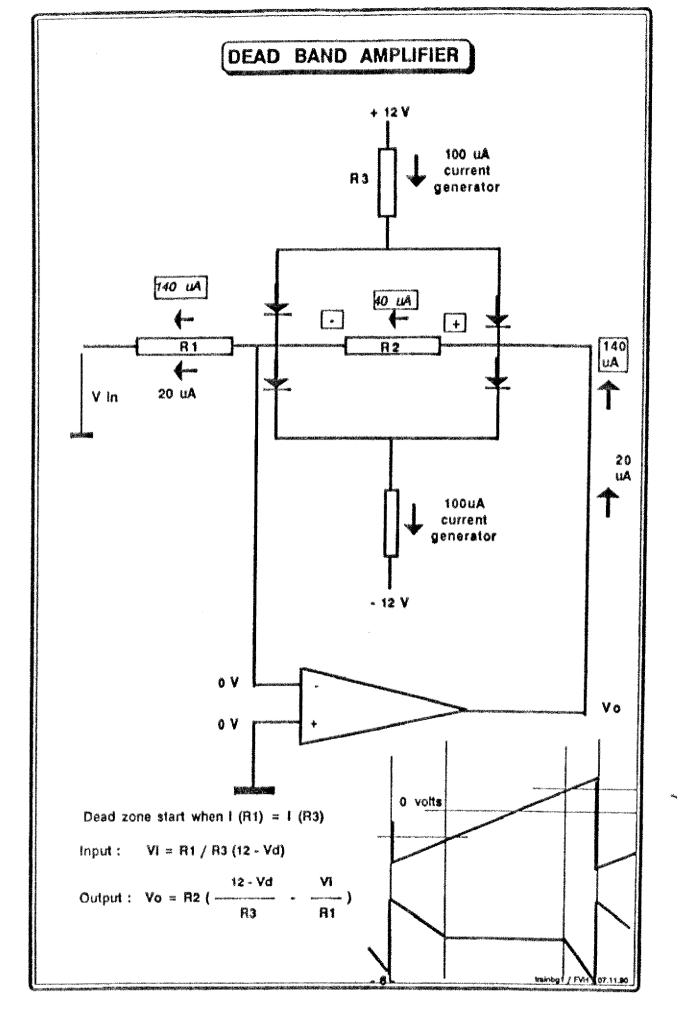

#### 6. ADJUSTABLE TOP AND BOTTOM BLANKING

The sub-unit generates blanking pulses for an adjustable blanking of the top and bottom

of the picture. To achieve a high accuracy, or, in other words, to dispose of a steep ramp, the sawtooth is sent into a "dead band response amplifier", built around the Opamp in IC8. The sawtooth enters pin 9 of IC8 on the sub-unit. The output is inverted and the ramp is steeper at the start and at the end. The two clipping levels are set by clamping circuits in order to obtain a complete feedback between these levels. As soon as the first clipping level is reached, the output is steady, and no output signal change is noted.

The resulting waveform is now sent to two level detectors in IC9(IC9 pin's 6 and 3). The clipping levels are regulated by the potentiometers in the Bellas, IC2 and IC3. The resulting top and bottom blanking exits IC9 pins 7 and 1, is added and then goes to IC10 pin 5. In IC10 it is mixed with a horizontal line pulse and exits pin 2. The signal now goes to the main board, to the base of Q20.

# 7. SIMULATION OF THE FLYBACK PULSE FOR THE PLL OF THE TDA2595.

A \* simulated "line flyback pulse is generated from the monoflop IC4. The first monoflop introduces a small delay for the pulse and the second monoflop standardizes the width of the pulse. The delay from the first monoflop is used to mislead the PLL IC and allow for a "negative" phase shift.

#### 8. BLANKING- COINCIDENCE.

In the event of non-coincidence of the sync and horizontal line pulse, or the absence of any Vertical Sync Signal transistor Q16 on the main board is completely saturated. This signal comes from IC7 pin 7, which is only low, when the line pulse and sync are locked to each other. In an unlocked condition, pin 7 is "high" and this turns on Q16 via R310. This results in:

- -Led D20 is illuminated to show the non-coincidence condition.

- If the blanking strap is in position, transistor Q15 is also saturated, and causes blanking of the three CRT's.

By removing the "blanking strap", the picture will not be blanked during non-coincidence.

If there is no Vertical sync, transistor Q5's base will be "high", causing Q5 to conduct, and via D5, the blanking and non-coincidence circuits will be activated.

Note: Blanking and non-coincidence are activated by horizontal unlock, or absence of vertical sync only. Therefore, if the vertical hold controls are maiadjusted, and the picture rolls vertically, it will not blank out. This "non-coincidence" signal is used by the controller board, to determine if the projector has an active source. In non-coincidence, the controller will display a message "no source, check input".

LITS

KIN CAL

FLYBACK

びとこの

VOLTAGE

Mary / 22227

# VERTICAL DEFLECTION UNIT

# VERTICA t OSCILLATOR AND SYNCHRONISATION

# SCAN FAIL LOOP / PROTECTION OF THE CRT

# BG-800 COMPONENT CLASS EHT BOARD

# 76-1742

# INTRODUCTION

On this board, the EHT drive pulses for the EHT power supply are generated. The primary circuit for the EHT power supply receives it's 300VDC supply from the Mains. In the event of failure, either because the EHT is too high, too much current in the EHT circuit or a horizontal or vertical scan fail condition exists, the EHT voltage is discontinued. We will discuss the generation of the EHT pulses, the EHT regulation, and the different protection circuits.

#### DC controlled multivibrator.

The EHT multivibrator is configured around two Schmidt Trigger NAND gates in IC2. Two time constants are involved in this circuit; C7/R11 and C8/R10 +Q2.

The first time constant is fixed, (C7/R11), whereas the second time constant is variable, depending on the current flow through Q2. Transistor Q2 acts like a variable resistor in parallel with R10. By varying the bias on Q2, and therefore it's resistance, the time constant can be varied (T=RxC)). Q2 is driven by the comparator transistor Q1. Q1 receives it's base bias voltage from FBHV (feedback high voltage from the divide by 1,000 circuit in the Splitter). The emitter of Q1 is set at +33 volts by zener Z1.

The duty cycle or the on/off time of the power switcher Q7, is regulated by the voltage difference detected by Q1, between the fixed emitter and the FBHV from the splitter. The frequency of this oscillator is typically 80kHz. This circuit keeps FBHV within a 1 to 2 volts of Z1 reference voltage.

The squared waveform at pin 3 of the NAND gate is, via a fast switching FET Q3, sent to the opto-coupler IC1. This opto-coupler is necessary because the remainder of the circuit is supplied with a +17M voltage and + 300 VDC Main which is not isolated from the Mains. The + 17M voltage DC is obtained from a special winding on the SMPS and the 300 Volts DC is the main bridge rectified mains voltage ( GNDM is " mains or hot ground ").

Caution: Any servicing on a board that uses both a Mains Ground and a Chassis Ground, should involve the use of an isolation Transformer, especially when using a "Scope", or other equipment connect to the main AC source. Do not connect

# the Main and Chassis Ground together at any time.

FET Q6 drives the push-pull stage Q4/Q5 and the pulses are capacitively coupled to the gate of Q7. The zener diode Z3 has two purposes. The negative level of the pulses are clamped at - 0.6 volts, and on the other hand limited to + 20 volts DC, in order to protect the switcher Q7. The transformer and the quadrupler are one in the same unit. The +300 volts DC from the main bridge, enters the board at J148A pin 22, and passes a filter L1/C19 and a fuse before it goes to the Quad at J148A pin 32 (+300HV).

#### **Protections**

#### a) EHT hold down:

The slider voltage of P2 (hold down adjust pot) is sent to the base of Q8 and Q8's emitter is set at 5.6 Volts by Z4. As soon as the EHT rises beyond 36.0 kV, the transistor Q8 starts conducting, turning on Q9. The schmidt trigger pins 8 and 9 of IC2 go high, and it's output pin 10, goes low. Diode D6 pulls the EHT multivibrator pin 5 on Ic2 low, and the multivibrator stops, halting the EHT. The output of IC2, pin 11 goes high at the same time and forward biases LED D8, to indicate a EHT hold down condition. The feedback resistor R30 keeps the hold down condition on (lock-down), until the projector is powered off to reset the circuit.

The EHT hold down must equally operate when there is an "open loop" situation, or no EHT feedback voltage from the splitter. If that were the condition, there would be no way for the circuit to monitor the EHT, and it could go higher than the 36.0 kV. The detection for "open loop" is built around the EHT "flyback" pulses on the drain of Q7. These pulses are rectified by D42 and the resulting pulsating DC is filtered by the PI-filter C30 and C12, and sent to Q10 base. As the EHT gets higher, the flyback pulses will increase in amplitude, and therefore the voltage to Q10 base will increase. From 5.6V and above Q10 conducts and via the opto-coupler ic3, the output pin 6 of the opto-coupler is switched low. This condition would exist if the amplitude of the pulses were excessive, or in other words, the high voltage was too high. This output is connected to Q8 collector, and pulls it low, turning on Q9, and the multivibrator is stopped as explained above.

# Note that Q10 is supplied by the +17M voltage ( not isolated from main or hot ground)

Finally, in the event of an excessive amount of CRT beam current, with a long duration, the duration determined by the time constant R102/C39, the collector of Q8 is pulled low via Q27, resulting in EHT hold down. The base of Q27 is connected to ground, and HVL is in the ground return of the Quadrupler, (see 76 1743 for HVL schematic), so as the emitter of Q27 goes more negative as the total beam current increases, Q27 is more forward biased and starts to conduct, pulling the collector low and activating the EHT hold

down. If any 1 CRT begins to draw too much current i.e. shorted CRT, through the "BCL" input, (coor. E6), Q27 again turns on causing HV holddown.

In conclusion, the EHT HOLD DOWN LED is " on " for :

- -too high EHT, information via the feedback FBHV

- -too high EHT in open loop via Q10 and opto-coupler IC3

- -too high total beam current lasting for some time via HVL

- -too high beam current in any one CRT via BCL

# b) Horizontal and Vertical Scan Failures:

In the event of a horizontal or vertical scan failure detected on the horizontal or vertical boards, the EHT multivibrator is stopped via D5. Scan fail is a "low" from the scan fail detect circuits. Via D5, the EHT is halted.

# c) Overcurrent protection:

The drain-source current of Q7 is measured by the resistor R21 in series with the source. This voltage is applied to transistor Q14 via a divider R40/R15. When this voltage exceeds 0.6 volts, Q14 starts to conduct and stops the EHT drive pulses by removing enable to IC1 pin 7, preventing damage to Q7 (pin 7 of IC1 is the enable pin , and must be "high" for the Ic to pass a signal). In this case , we have no illumination of the EHT hold down LED.

# Slow startup of the EHT.

When the projector is switched on, a slow startup of the EHT voltage is provided. This is accomplished by the circuit around transistor Q11. The voltage for the reference zener Z1 is taken from the + 230 volt line through R7. When the unit is switched on, capacitor C4 charges up via R7 and C40 charges through R43. Until C40 fully charges, PNP transistor Q11 will be forward biased and inhibit C4 from charging. This gives a slow rise to the voltage for Z1, and this is the voltage that the FBHV is referenced to, so therefore the EHT will also have a slow rise.

When the unit is switched off, C40 is rapidly discharged via D9 because the 230VDC line drops quickly, taking the EHT reference voltage on Z1 quickly down, and therefore the EHT itself goes down. C40 discharging turns on Q11 because it's base is pulled in a negative direction. If a scan fail signal is present, Q13 sees a (low) causing Q13 which is normally biased on to go off. The base of Q12 then goes "High " and C40 is discharged, pulling down the reference voltage, through the conduction of PNP transistor Q11.

The EHT is stopped during scan fail by J148A pin 4 going low, and through D5, stopping the EHT multivibrator. If the scan fail is removed, we are back to a slow start condition because Q13 base would go High, saturating Q12, and thereby discharging C40 and C4.

FET Q30 is used to keep a drive pulse from driving Q7, until the drive voltage from the preceding pulse is zero. The EHT pulse is coupled to the gate of Q30 and removes the high on the enable pin (pin 7) of lc1 until the drive pulse is zero, turning off Q30. Then the next pulse can pass.

To adjust either the High Voltage P1 or HV holdown P2, an accurate high voltage probe must be used. A probe is available from Barco, complete with a connector that will safely connect to the splitter. Failure to use the correct type of probe can cause the following:

- 1. Inaccurate high voltage settings causing; poor picture, abnormal CRT wear, arcing potential, excessive tube radiation.

- 2. A SHOCK HAZARD. the EHT is set at 34.7kv, AND THIS VOLTAGE IS WELL REGULATED. A shock from this supply, due to an improperly designed, hand held HV probe, could result in severe injury to the technician.

When adjusting either P1 or P2, these components must be replaced with new parts, and after setting the pots, they must be glued and white safety covers attached.

# **BG-800 COMPONENT CLASS**

# SM POWER SUPPLY 76 1770

## The switch mode power supply:

The switched mode power supply derives all the necessary DC voltages and isolates them from the incoming main voltage from the AC line.

The first section of the power supply to start up is the plus and minus 9 volt standby power supply. It provides the controller board with the necessary voltages to operate the controller board circuitry so that the control IC's on the controller board will be active to read the information from the RCU or the built in controller.

The second section of the power supply delivers all the stable or fixed DC voltages and it is built around IC102, Q101, and T2.

The third part of the power supply produces the HTHD which is the frequency dependant voltage that is fed to the Horizontal sweep circuitry. This is built around IC100, Q100, and T1.

# 1. Principle of the switched mode power supply:

The principle of the switched mode power supply is as follows

When a positive pulse is applied at the base of switching transistor Q101, a current flows through the primary winding of transformer T2, supplied by the 300 Volt DC input bridge rectifier, through F100 to P19. When the switching transistor is cut off, the energy stored in the primary field is transferred to the secondary winding of the transformer, rectified by the diode D201, in case of the + 17V, and filtered by C202 and C203. The filter has a low reactance at the operating frequency and in effect shunts the AC ripple to ground and leaves the DC component. By adjusting the duty cycle of the on versus off time of the switching transistor, we can adjust the amount of energy that is stored in the primary field and transferred to the secondary, thus controlling the secondary output voltage. The IC used to regulate the DC voltage and the duty cycle is a specially designed IC, a TDA 4601.

One of the principle advantages of a SMPS is that the frequency of operation is much higher than a power line frequency type of power supply which permits the use of much

smaller transformers and filter capacitors.

# 2. Start Up.

When the projector is switched on with the main power switch, the 110VAC is connected to a input doubler circuit which in effect doubles the 110VAC to 220 VAC. This voltage then goes to the fullwave bridge rectifier (D100-D103), and the rectifier delivers +300 VDC to the power supply transformer primaries. This 300 VDC starts a free running oscillator, composed of Q1 and Q2 and T1, on the subunit (coor.B 1-2) Pins 11 and 12. The grounds of the secondary of T1 are connected to Cold ground, so that should be corrected if necessary in the service manual. The + and -9 volts are developed from D1 and D2 and C4 and C5 and zeners Z1 and Z2 are used to regulate the output to + and -9 volts DC.

The plus and minus 9 volts is sent to the controller board for standby power.

When the on/off signal (J4 pin 3 sub-unit coordinate B-4) produced by the orange standby button on the control unit, becomes "low", the LED of the opto-coupler Ic1 will light up and Q3 will be cut off because the base of Q3 is pulled to ground. This will allow the gate of Thyristor THYR1 to go positive and turn on the Thyristor (gate controlled diode), causing 11 volts DC to be connected through D104 to IC100 and IC 102 pins 9, turning on the both IC's. Once Ic102 is operational, the voltage on the secondary winding of T2 (P22, P24) will provide the operational voltages for the two IC's. Once this happens, D104 sees 13 volts DC on its cathode, and it becomes reversed biased. At this point the cathode voltage of THYR1 is equal to the gate voltage, and THYR1 turns off.

The time constant of R113-C113 on IC100 is longer than the time constant of R130-C121 on IC102. The IC will not start until pin 1, the reference pin reaches 4.4 VDC. C121 delays this charging of pin 1, and therefore this causes a **slow start** of the IC. The C113 connected to pin 1 of Ic100 is much larger than C121. This results in a slower startup of IC100 to make sure that the HTHD voltage is only available after the supplies controlled by IC102 and T2 are already on and stable.

When the projector is turned to the standby condition, the on/off (J4 pin 3) signal becomes "High" turning off Ic1, and Q3 on the subunit turns on. This pulls down pin 5 of IC102 (external blocking pin) which shuts off IC102 through D105. Pin 5 is the input on the TDA 4601 that monitors the main voltage and if it goes too low (below 5.5VDC), the IC will shut off. The monitoring of the 300Volts DC is through the divider R123, R122. If IC 102 shuts off, the supply to pin 9 of IC100 will also be turned off, disabling both IC's. This will leave only the standby power supply operating.

# 3. Control loop of the stable or fixed voltages.

All the stable or fixed voltages are delivered by the first part of the Switched Mode Power Supply, formed by IC102, Q101 and T2. The secondary winding P20-P22 of T2 provides a negative feedback voltage after rectification through D111-C118-C119. A reference voltage, coming out of pin 1 of IC102, comes up slowly through R130-C121, providing a slow start to the switch mode.

A simulation of the collector current of Q101 is made by charging C117 through R124 from IC102 pin 4. This creates a sawtooth ramp voltage and the switching point of the IC is determined by the control voltage on pin 3, the control pin. When the voltage on C117 reaches a certain level, the capacitor is discharged by the control logic of IC102.

The higher the control voltage on pin 3 of the TDA4601, the higher on the sawtooth ramp before the IC pulses Q101. Therefore the feedback voltage from pin 3, will modify the the pulse width of the driving pulses.

The negative feedback voltage developed by D111 is compared with the reference voltage in the voltage divider network through R131-R125 and P100, the 17 volt adjust pot. This combined voltage is fed into pin 3 of IC102 and by adjusting P100, we can adjust all the secondary voltages developed by T2.

A feedback signal is fed through R127 to IC102 to provide a zero passage identification for making the SMPS more efficient. This zero passage insures that the only time the transistor is switched is when there is no energy in the field in the transformer. From this AC voltage sent to pin 2 of the TDA4601, the IC can determine when the current in the transformer is crossing the Zero point.

Divider network R122-R123 provides an input voltage to pin 5 of the TDA 4601, which is relative to the 300VDC main supply, to turn the IC off in case of the Main input voltage dropping too low. Pin 5 must be at least 5.5 VDC for the IC to operate. If pin 5 drops below 5.5VDC, pin 7 goes to ground and grounds the drive pulses from pin 8, thereby turning off the supply.

Diode D112 is connected to winding P18 and produces 17V DC referenced to Main or HOT ground. This supply is only used by the EHT generator board because that board also is connected to the Main 300V DC input. .

# Control loop of the HTHD ( Horizontal Deflection High Voltage).

The supply voltage for the horizontal deflection circuit has to change, when the horizontal frequency of the projector changes. A separate power supply is provided to deliver this voltage. This supply is formed around IC100, Q100, and T1.

The reference voltage of IC100 pin 1 is also integrated by means of R113, C113, to provide a delayed start. The width of the driving pulses produced by IC100 can be varied by modulating the voltage on pin 3 of that IC. When the voltage on pin 3 is lowered the duty cycle will be shorter and less energy will be sent to the transformer to regulate the voltage. The (FBHD) feedback voltage is used for this purpose. The FBHD is the feedback Horizontal Deflection voltage from a transformer on the Horizontal Deflection board. This primary of this transformer is connected across one of the horizontal deflection yokes, and the secondary output voltage is rectified and is proportional to the width of the raster on the CRT.

The secondary winding P13-P17 provides the zero passage identification through R109-R110-R111 and over voltage protection through D108-C108-Z101. As soon as the rectified negative voltage across C108 passes (51+5) 56 volts, pin 5 is pulled low and IC100 switches off.

#### 5. Feedback control of HTHD.

The feedback loop consists of a 5mA current source (Q7), Z7, and a controlled reference voltage ( Z8, R28 ,R29 ) and a opto coupler IC5. This is located on the sub-unit schematic.

The current source supplies Z8 with 5 mA to achieve a HTHD independent reference voltage. Z7 is connected between the collector and emitter of Q6, and limits the C-E voltage across Q6 to 7.5 V DC., minus the drop across Ic5, D10, the Green LED, and R37.

FBHD (Feedback Horizontal Deflection J4 pin 7 sub-unit) is a rectified positive DC voltage proportional to the current flowing through the deflection coils. This voltage modulates the current through Q6 which in turn controls the current through the opto-coupler LED, pins 1 and 2 of IC5. When the FBHD increases, due to a higher deflection current, the current in Q6 increases. This causes an increase in IC5 LED current which causes the transistor in IC5 ( pins 4 and 5 ) to increase it's conduction, and in turn the FB2 voltage to IC100 pin 3 is pulled towards ground. This results in shorter driving pulses for Q100 and a lower secondary voltage output voltage.

E (FBHD) increases

I Q6 increases

I IC5 increases

E IC100 pin 3 decreases

E HTHD decreases

# 1. Protection against a disconnected FBHD loop

The problem with an open feedback loop is that the control voltage is lost and the IC may think that the cutput voltage of the circuit is much too low and try to increase it, when in fact the voltage may be actually too high. When the FBHD voltage is not connected to IC4 pin 5, the non-inverting input of IC4 goes low, causing the output of IC4, pin 7 to go low. This low voltage forward biases Q8, and pulls the emitter of Q8 to ground, which turns on the LED in IC5. This will lower the voltage on pin 3 of IC100 and lower the HTHD voltage to about one-half it's normal value. This low voltage will be insufficient to produce horizontal scan, and the projector will go into "scan fail".

# 2. Protection against undervoltage of the +17 volt supply.

To prevent damage to the Power-Mosfets of the Horizontal Deflection circuit, the + 17V supply must not drop below 14 volts. The Power-Mosfets are driven by circuitry supplied by the 17V supply. If the 17 volts is too low, the Mosfets are not fully turned on, due to insufficient drive, and the internal resistance will be too high, causing them to overheat. When this happens, the HTHD must be switched off immediately.

The + 17v supply is compared with a reference voltage in IC3, (pins 5, 6, and 7). This reference voltage is derived from the +30v supply and clamped by adjustable zener Z6. Pot P1 is set for 14V, and when the 17 volt supply goes below 14 volts, pin 7 of IC3 goes low and turns on Q8 through D7 and the HTHD goes to about one half it's normal value. R17 and D6 prevents oscillations in the circuit. The 30V DC line is used for the reference voltage, since it would have to drop almost in half, to make the reference voltage inaccurate for circuit operation.

# 3. Overvoltage protection.

A high voltage protection is provided around pins 1-2-3 of IC4 and transistor Q9. The HTHD voltage is divided across resistors R38 and R39, and compared to a reference voltage formed by R40 and zener diode Z10 from the 30 volt line. When the HTHD becomes too high, the output of IC5 (pin 1) will go high, and trigger Q9. Q9 causes the LED in the Ic5 to turn on, and pull pin 3 of Ic100 low, and greatly reduce HTHD. The HTHD goes to about one half it's normal value in this condition. The unit has to be powered off, to reset the circuit, because the diode D8 locks this condition on by holding pin 3 of Ic4 high, until the unit is powered off.

# 4. Overcurrent protection.

To protect Q100 and Q101 on the main board against excessive current flow, the voltage across R106 and R121 are compared with the internal reference voltage of IC100 and IC102 in the Op-Amp IC101. When the current becomes too high, causing a higher voltage across either R121 or R106, which are in series with the emitters of Q101 and Q100, IC101 pin 1 or pin 7 goes low and pulls down pin 3 of IC100 or IC102. This shuts

down the supply that has the excessive emitter current flow.

# 5. The horizontal amplitude regulation.

The Horizontal Amplitude voltage which is adjusted by means of the projectors remote control, controls the reference of Z8 through IC3 (pins 1, 2, and 3) on the sub-unit. When the amplitude of the voltage increases on inverting input pin 2 of IC3, the control voltage to Z8 will decrease and the reference voltage on Z8 will rise, which decreases the conduction of Q6 by setting the emitter to ground voltage of Q6. This will cause the LED in IC5 to conduct less, and pin 3 of IC100 will rise. The driving pulses for Q100 will be extended, and the output voltage HTHD will rise, causing a wider horizontal deflection.

We can limit the maximum amount of current that will flow through the horizontal deflection coils by adjusting P2. This will determine the conduction point of Q6, and therefore the maximum amplitude of the Horizontal Width. The HTHD voltage should be set using composite video. After checking to make sure the throw distance is accurate, display composite video on the screen, adjust the horizontal size to 99 on the bar scale, and with the blanking fully open, adjust P2 on the sub unit, until the video slightly overscans the screen. HTHD should then read between 47VDC to 52 VDC.

# **BG-800 COMPONENT CLASS**

# **QUAD DECODER**

# 76 1753 76-1822

#### Introduction.

The composite video signal is split up into a luminance signal and a chrominance signal, and processed separately. The S-VHS signal is already separated at the source and processed the same as the composite signal.

The luminance goes through a enhancing or sharpness circuit, and the chroma information is blocked. The luminance then goes to IC4, containing the luminance delay line. (TDA 4565)

The chrominance information passes the correct bandpass filter and reaches pin 15 of the quad decoder IC2 ( TDA 4557 ).

The NTSC 3.58Mhz passes the comb filter ( DL1) before entering pin 15 of IC2

The color difference signals are then regulated in amplitude by two potentiometers in IC3 (Bella), and then go to IC4.

The Y signal, the R-Y and B-Y signals are processed and the RGB signals are matrixed and leave the decoder board, and go back to the RGB Analog and Switching Board for text insertion.

The brightness and contrast control is accomplished on this board. Then the signals are ready for the RGB power drivers.

In case of the 76-1822 Quad Decoder with Gain control, the Red and Blue black level and gain is adjusted on the sub-board, as well as brightness and contrast.

The CP clamping pulse is formed to be utilized in the brightness control circuit and on the RGB switching board.

The blanking pulses for the horizontal retrace time, and the adjusted left/right blanking ( user adjusted), are combined with the vertical blanking pulses produced on the UN SYNC + VERT deflection board in order to get a total blanking pulse train which is then sent to the RGB driver output boards.

We will now cover these items in more detail.

# 1. Video Composite Signal Flow.

# Enhancing;

The composite video arrives at the base of the buffer Q1 and feeds the delay line DL3. The middle tap of this delay line supplies the base of the buffer Q2.

The signal then goes from Q2 emitter to the chrominance bandpass filters PAL/N4 and SECAM, and to a buffer in IC1 ( Pins 12, 13 and 14).

The output, pin 13 of DL3 is delayed twice as much as the pin 8 output, and obviously at the node C3/C4, we obtain the sum of the delayed and non-delayed signals.